Pentium 2 Architecture Block Diagram

Externally pentium 4 transfers four data per clock cycle.

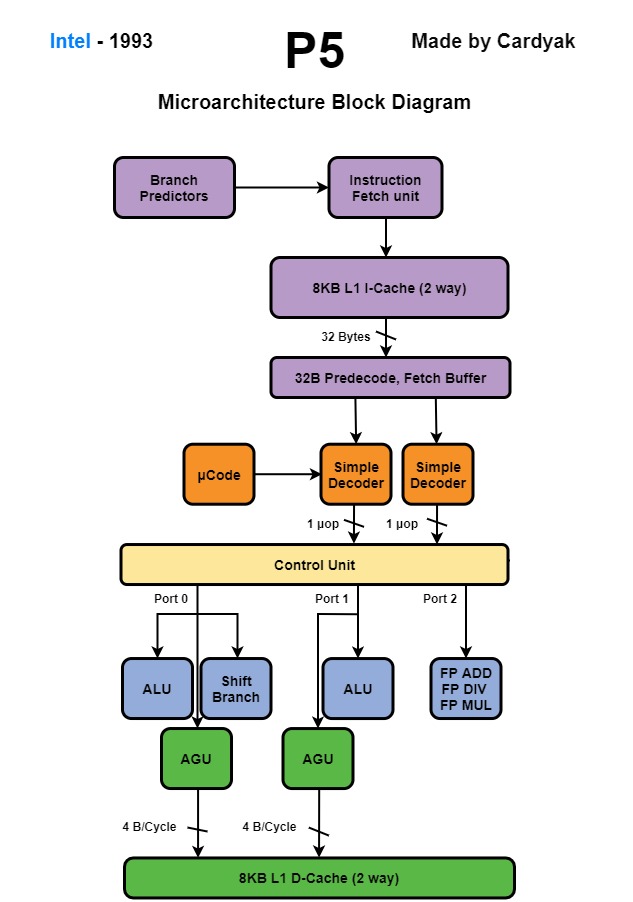

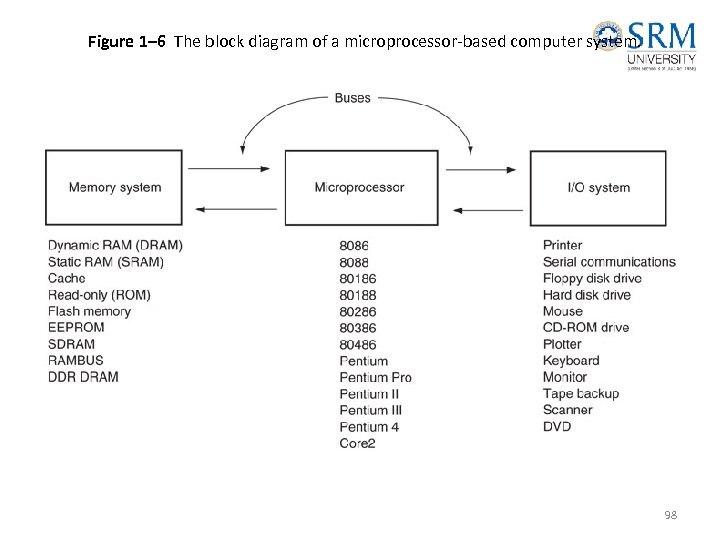

Pentium 2 architecture block diagram. Pentium 4 processor block diagram fp rf fmul fadd mmx sse fp movefp move fp store 32 gbs system interface l2 cache and control l1 d cache and d tlb store agu load agu schedulers integer rf alu alu alu trace cache renamealloc alu uop queues btb ucode rom btb i decoder 3 3 tlb. Simplified block diagram of processor tap logic. Pentium ii processor system bus data integrity architecture. The pentium family of processors originated from the 80486 microprocessor.

Here are the basic differences between pentium 4 architecture and the architecture from other cpus. Real mode architecture pentium supports two modes real mode uses 16 bit addresses runs 8086 programs pentium acts as a faster 8086 protected mode 32 bit mode native mode of pentium supports segmentation and paging. It runs at a clock frequency of either 60 or 66 mhz and has 31 million transistors. It has 12 stage super pipelined implementation whose efficiency is 33 higher than that of pentium.

Tap controller finite state. This is an ia 32 architecture which means that the internal registers are 32 bit long. Bus signals protected directly. As per msbte syllabus introduction to pentium processor salient features of pentium system architecture superscalar execution.

Pentium 4 block diagram. Introduction to intel architecture executive summary the term intel architecture encompasses a combination of microprocessors and supporting hardware that creates the building blocks for a variety of computing systems. Pentium ii processor developers manual 243502 001 october 1997 1997. Some of the features of pentium architecture are.

The term pentium processor refers to a family of microprocessors that share a common architecture and instruction set. Although the architecture is straightforward and remarkably well supported the. In order to get a closer look at how the p6 family micro architecture implements dynamic execution figure 2 3 shows a block diagram of the pentium ii processor with cache and memory interfaces. Superscalar architecture dynamic branch prediction pipelined floating point unit separate 8k code and data caches writeback mesi protocol in the data cache 64 bit data bus bus cycle.